在大规模集成电路(VLSI)设计中,复位电路是确保芯片从初始状态开始正确、稳定运行的基石。它不仅是芯片上电后的首个关键操作,也是在系统出现异常或需要重启时恢复功能的保障。随着工艺节点不断演进,芯片集成度与复杂度呈指数级增长,复位电路的设计面临着前所未有的挑战,其性能与可靠性直接影响着整个系统的成败。

复位电路的核心作用与基本架构

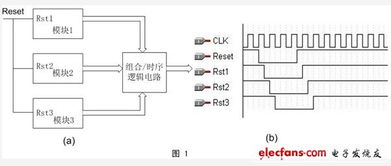

复位电路的主要功能是初始化芯片内部所有时序逻辑单元(如触发器、寄存器)到一个已知的、确定的状态。一个典型的复位系统通常包含以下部分:

- 复位信号生成器:通常是一个上电复位电路,监测电源电压,在电压达到稳定阈值后才产生有效的复位信号,避免因电源爬升过程中的毛刺导致逻辑误动作。

- 复位信号分布网络:将全局复位信号低偏斜、低抖动地传递到芯片各个角落的数百万甚至数十亿个时序单元。

- 局部复位同步与去抖:在时钟域交界处,对复位信号进行同步处理,防止亚稳态传播;同时滤除可能由噪声引起的短暂复位脉冲。

传统的复位设计多采用异步置位/复位(Asynchronous Set/Reset)的触发器,并搭配全局复位树。这种方法在纳米级工艺下面临严峻考验。

现代VLSI设计中复位电路面临的主要挑战

- 功耗与面积开销:庞大的复位分布网络本身消耗可观的动态功耗和静态功耗(漏电),并占用宝贵的布线资源与面积。在低功耗设计中,这部分开销变得不可忽视。

- 时序收敛与信号完整性:随着时钟频率提升和工艺尺寸缩小,确保复位信号与时钟信号一样,在极低的偏斜和抖动下到达所有端点,变得极其困难。复位路径上的串扰、电压降(IR Drop)和工艺偏差都会影响复位释放的同步性,可能导致系统初始化不一致。

- 多时钟域与低功耗模式:现代SoC包含数十乃至上百个时钟域,且支持动态电压频率调节(DVFS)和电源门控。如何在这些复杂场景下安全、高效地管理和撤销复位,避免跨时钟域问题和部分掉电区域的复位失效,是一大难题。

- 测试与可观测性:复位电路的缺陷可能导致系统性故障,但其本身难以通过传统的扫描链进行充分测试,需要专门的可测试性设计(DFT)策略。

复位电路的创新改进方向

为应对上述挑战,学术界与工业界提出并应用了多种改进方案:

- 复位架构优化:

- 分级与分区复位:取代单一的全局复位,根据功能模块的重要性、电源域或时钟域进行分区。非关键模块或常开模块可以采用局部复位,仅在必要时动作,减少不必要的功耗和干扰。

- 复位信号复用与压缩:利用现有的时钟树或电源网格进行复位信号传输,或采用编码技术减少复位控制线的数量。

- 低功耗复位技术:

- 复位门控:在模块不工作或进入休眠状态时,关闭其复位网络的开关,切断动态功耗和漏电路径。

- 基于存储器的初始化:对于大型存储阵列(如SRAM),采用内置自测试(BIST)或预载已知数据模式的方式替代硬件复位,更为高效。

- 增强鲁棒性与可靠性:

- 智能复位序列:引入片上状态机,控制复位的申请、同步、撤销序列,确保不同电源域和时钟域按正确顺序完成初始化,防止竞争冒险。

- 自适应复位延迟:根据实际监测到的电源稳定情况或时钟锁定状态,动态调整复位脉冲宽度,提升对工艺、电压、温度(PVT)变化的容差。

- 软复位与局部复位:在系统运行中,允许通过软件配置对特定功能块进行复位,而不影响整个系统,提升了调试和错误恢复的灵活性。

- 设计与验证方法学改进:

- 在电子设计自动化(EDA)工具中加强对复位路径的静态时序分析(STA)和电源完整性分析。

- 采用统一功率格式(UPF)等标准来规范多电压域下的复位策略。

- 在验证阶段,构建全面的复位场景测试用例,包括上电、下电、异常注入等,并利用形式化验证检查复位状态机的正确性。

###

复位电路,这个看似基础的功能模块,在现代超大规模集成电路设计中已演变为一个涉及系统架构、低功耗设计、信号完整性和可靠性的复杂子系统。其设计不再是简单的信号连通,而是需要从芯片顶层进行周密规划与协同优化。随着三维集成、芯粒(Chiplet)等新技术的发展,复位电路的设计将需要进一步考虑跨芯片、跨介质的同步与协调问题。持续的技术创新与方法改进,是确保集成电路巨轮在每一次启航时都能稳健、准确朝向目标前进的关键所在。