集成电路芯片,作为现代电子设备的心脏,其成本构成远比表面看到的硅片价格复杂。从一粒沙子到一枚功能强大的芯片,其成本涵盖了设计、制造、封装测试以及知识产权等多个维度。理解这些成本要素,有助于我们洞察半导体产业的定价逻辑与技术壁垒。

一、设计与研发成本:高昂的“智力”投入

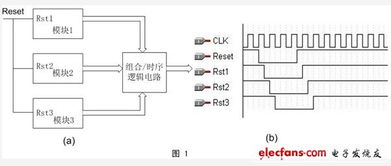

芯片的成本首先源于其设计与研发。这是一个资金与技术密集的先行阶段,成本极高且具有高风险性。

- 人力成本:一支由架构师、设计工程师、验证工程师等组成的顶尖团队,其薪酬是主要开支。

- EDA工具授权费:芯片设计必须使用昂贵的电子设计自动化(EDA)软件,其年度授权费用动辄数百万甚至上千万美元。

- IP授权费:为了缩短设计周期,设计公司常需购买成熟的IP核(如ARM处理器核心、接口协议等),这也是一笔不菲的固定支出。

- 流片(Tape-out)费用:设计完成后,需要交付晶圆厂进行首次试生产以验证设计,单次流片费用可能高达数百万至数千万美元,且不保证成功。

这部分成本需要分摊到最终成功量产并销售的所有芯片中。芯片越复杂、工艺越先进,设计和研发成本就越是呈指数级增长。一款先进制程的高端处理器,其研发投入可达数十亿美金。

二、制造成本:核心的“物理”开销

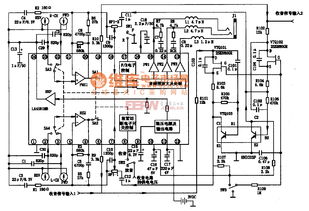

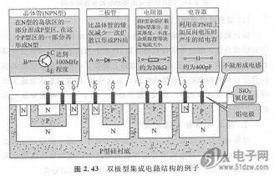

制造是在晶圆厂(Fab)完成的环节,其成本主要由以下几部分构成:

- 晶圆成本:即硅片本身的材料成本,晶圆尺寸越大(如12英寸对比8英寸),单位成本效益通常越高。

- 工艺制程成本:这是制造的核心成本。工艺越先进(如5纳米、3纳米),所需的光刻、刻蚀、离子注入等设备越昂贵,工艺流程也越复杂,导致每片晶圆的加工成本急剧上升。光刻机(如EUV)单台售价就超过1亿美元。

- 良率(Yield):并非所有在晶圆上制造出来的芯片都是可用的。良率是指合格芯片所占的比例。良率越低,意味着每个功能完好芯片所分摊的制造成本就越高。提升良率是晶圆厂的核心竞争力之一。

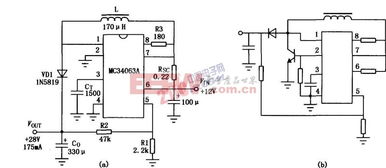

单个芯片的晶圆制造成本可以粗略用以下公式估算:

芯片成本 ≈ 晶圆价格 / (每片晶圆产出的芯片数量 × 良率)

其中,每片晶圆产出的芯片数量取决于芯片尺寸(Die Size)和晶圆尺寸。

三、封装与测试成本:最后的“包装”与“质检”

从晶圆上切割下来的裸片(Die),必须经过封装和测试才能成为可销售的芯片。

- 封装成本:将裸片封装在保护性外壳中,并引出连接引脚。封装形式多样(如QFN、BGA、CSP等),越复杂、集成度越高的封装(如先进封装、3D封装),成本也越高。

- 测试成本:对封装后的芯片进行功能和性能测试,筛选出合格品。测试设备昂贵,测试程序开发与测试时间也构成成本。

四、其他重要成本因素

1. 知识产权与专利:芯片可能涉及的专利许可费用。

2. 营销与销售成本:市场推广、渠道建设等费用。

3. 固定资产折旧:晶圆厂和封测厂的巨额建设投资(一座先进晶圆厂造价可达百亿美金)需要按年限折旧,分摊到每片晶圆或每个芯片上。

4. 规模效应:当芯片产量巨大时,高昂的前期设计、研发及设备折旧成本被极大摊薄,导致单颗芯片成本显著下降。这正是很多消费级芯片在生命周期后期价格走低的原因。

****

集成电路芯片的成本是一个多层次的复合体。对于先进的高性能芯片(如CPU、GPU),设计和研发成本主导了总成本;而对于成熟制程的量大面广芯片(如某些MCU、电源管理芯片),制造成本和封装测试成本占比更大。芯片的最终价格,则由其总成本、市场供需关系、竞争格局以及厂商的战略定位共同决定。理解这些成本构成,不仅能看懂芯片定价,更能深刻理解半导体行业技术密集、资本密集、高度依赖规模经济的本质特性。